Until now, I have been held back by the prices of the Xilinx boards we used back then.

Since second year of University, I have been wanting to use our VHDL and FPGA course for some FPGA projects at home. Additional Informationįurther design support, product tutorials, application notes, users guides and other documentation can be found on the Lattice website at. The Verilog and VHDL testbenches illustrate the use of “for-loops” to generate test vectors and signal delays. This design demonstrates the use of a configurable FIFO module in both Verilog and VHDL using the Lattice Diamond Design Software. Diamond can be used as a stand alone development environment with alternative synthesis and simulation software.

LATTICE SYNPLIFY PRO MF515 ERROR SOFTWARE

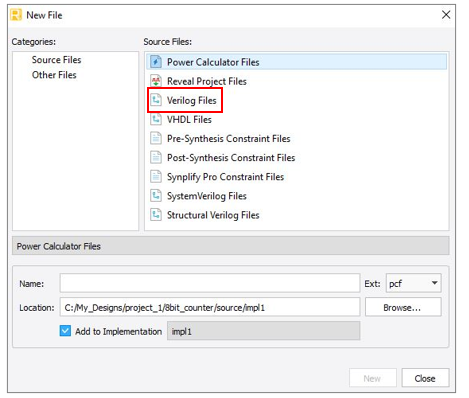

Lattice Diamond version 2.0.1 was used to develop the “FIFO.vhd” and ”FIFO_v.v” with supporting software from Synopsis (Synplify Pro for Lattice) and Aldec (Active-HDL Lattice Edition). The test bench provided should cover most test cases. The testbench was then modified to include various test cases to exercise the condition flags and ensure proper read and write pointer control. The included test bench was created from the “generate test bench template” command in the “HDL Diagram” window. The FIFO Verilog implementation HDL block diagram from the Lattice Diamond “Generate Hierarchy” function can be seen in figure 2 below.įigure 4 – FIFO Aldec Active HDL Testbench Output The VHDL generated black box model with inputs and outputs can be seen below in figure 1.įigure 1 – Black Box Diagram for FIFO Buffer The design has a data input port, a clock, active low reset, read enable, write enable, data output port, data count port, empty, full, almost empty, almost full, and error signals. The watermark flags can be set to trigger at various depths by adjusting the ALMST_F and ALMST_E parameter values. The output word width can be scaled as can the FIFO address space. The FIFO_v.v and FIFO.vhd can be configured by changing the values within the parameterization and generic parameters respectively within each module. Lattice Diamond Design Software version 2.0.1 with third party software Synplify Pro for Lattice and Active-HDL Lattice Edition. The Software required/used for this design: As the port name suggest, this tells the world (outside the module) how many words are currently stored between the read and write pointers within the RAM. There is an output port for reading out the data count.

LATTICE SYNPLIFY PRO MF515 ERROR FULL

The FIFO also has flags for empty, full and error. The depth of the “almost full” and “almost empty” flags can be adjusted within the module’s parametrization, or generic block in the case of the VHDL version. There are watermark flags available for “almost full” and “almost empty” conditions. The FIFO module is a variable-length buffer with scalable register word-width and address space, or depth. The FIFO.vhd and FIFO_v.v modules are verified in testbenches by writing and reading values to and from the FIFO while observing the RAM data and the condition of the output flags. If available, the tools will use the embedded block RAM resources within the FPGA. For example, a FIFO module can be used as a circular buffer or delay line in a FIR filter. This module (in both Verilog and VHDL) is a First-in-First-Out (FIFO) Buffer Module commonly used to buffer variable-rate data transfers or to hold/buffer data used in digital communication and signal processing algorithms.

Overview of the FIFO Buffer Module and common usage.The following topics are covered via the Lattice Diamond ver.2.0.1 Design Software.

0 kommentar(er)

0 kommentar(er)